舊聞新看:一文看懂算力核心HBM的技術特點

DDR就是雙倍速率。

以1600MHz的內存條為例,X64的位寬,帶寬就是:

1600MHz*2倍速率*64bit/8/1000=3.2*8=25.6GB/s;

以8Channel的Intel ICX處理器為例,帶寬可以達到8*25.6GB/s=204.8GB/s;

以8Channel的AMD ROME處理器為例,帶寬可以達到8*25.6GB/s=204.8GB/s。

以1333MHz的內存條為例,X64的位寬,帶寬就是:

1333*2倍速率*64bit/8/1000=2.666*8=21.328GB/s;

以6Channel的Intel SKL處理器為例,帶寬可以達到6*21.328GB/s=127.968GB/s。

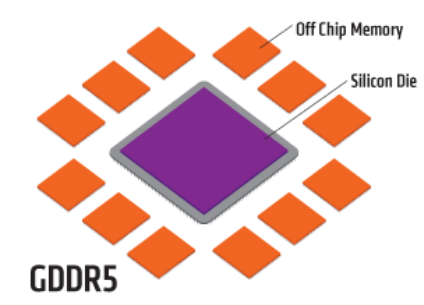

GDDR可以做到四倍速率。

以1750MHz的內存為例,單個顆粒X64的位寬,帶寬就是:1750MHz*4倍速率*64bit/8/1000=7*8=56GB/s;

以Nvidia Geforce GTX 1080 Ti為例,使用了11GB的GDDR5X,內存時鐘是2750MHz,4倍頻,內存頻率是11GHz,內存位寬是X352bit,那么內存帶寬為:2750MHz*4倍速率*352bit/8/1000=484GB/s;

以Nvidia Geforce RTX 2080 Ti為例,使用了11GB的GDDR6,內存時鐘是3500MHz,4倍頻,內存頻率是14GHz,內存位寬是X352bit,那么內存帶寬為:3500MHz*4倍速率*352bit/8/1000=616GB/s;

![]()

優點是帶寬比較高,功耗比較低。

缺點是,適合并發,不適合隨機訪問;時序復雜,工藝要求高;不適合配合CPU的Cache line的讀取。

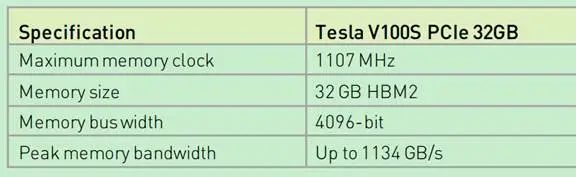

HBM雙倍速率,但是堆疊提高位寬。

2013年是HBM,2016年是HBM2,優勢在堆疊,通過TSV和基底通信,每個die有2個128bit位寬的Channel,4層堆疊叫做4-Hi,帶寬可以達到4*2*128=1024bit。

HBM以500MHz的內存為例,單個顆粒的帶寬可達到:500Mhz*2倍頻*2Channel*128bit*4Die/8/1000=1GHz*1024bit/8=128GB/s;

HBM2時鐘加倍,以500MHz的內存為例,單個顆粒的帶寬可以達到2*128GB/s=256GB/s。

以Nvidia Tesla V100S為例(GPU和HBM之間使用硅中介進行2.5D的封裝)。

應當是使用了4顆,帶寬為:1107MHz*2倍頻*4096bit/8/100=1113.568GB/s,HBM的優勢封裝比較小,堆疊設計。缺點是TSV工藝造成成本比較高。

HBM(High Bandwidth Memory)和DDR一樣都是一種硬件存儲介質。DDR被廣泛應用于CPU與各種硬件處理單元的外掛存儲設備,那么既然DDR4已經作為成熟存儲介質,為什么要推出HBM存儲設備?主要原因在于DDR4現有吞吐能力不能滿足當今計算需求,尤其是在AI計算、區塊鏈和數字貨幣挖礦等對大數據處理訪存需求極高等領域,DDR4的吞吐能力更顯薄弱。

所以,HBM以其高吞吐高帶寬的優勢,活躍在工業界和學術界。比如在學術領域,尤其在DSA(Domain Specific Acceleration)場景,如果能將embedding數據合理分配到32路HBM當中,同時做到系統級pipeline數據訪存和計算,那么都會有比較優秀的加速效果。

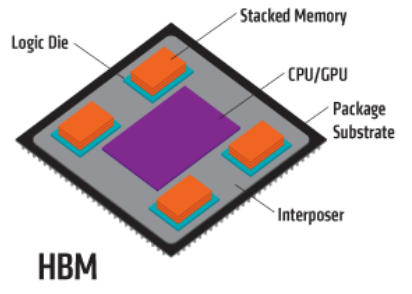

HBM帶寬

我們一直在講HBM帶寬比DDR有優勢,那么具體是什么優勢?

DDR4帶寬——ddr4數據位寬是64bit,以時鐘頻率2400MHz為例,那么帶寬為:2400M*64 =153.6Gbps。

HBM帶寬——HBM應用axi3協議,數據位寬為256bit,時鐘頻率可達450MHz,數據通道為32路,那么對于一塊FPGA外掛一個HBM的硬件設備,其數據帶寬為:450M*256*32=460.8Gbps。

所以,在不考慮CPU和FPGA區別的前提下,一塊帶HBM的FPGA要比普通CPU服務器性能高上3倍左右,當再考慮CPU cache miss和DDR使用效率的時候,帶有HBM的FPGA所帶來的帶寬增益將會更大。

但是單塊HBM的內存大小一般最大為16GB,而單個DDR4普遍能做到64GB。所以當業務所需數據量較大時,將不再適合只將訪存數據存儲在HBM中。

HBM細節

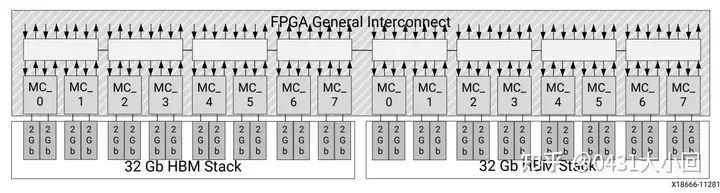

HBM分為2個stack,每個stack有8channel,每個channel可以分為2個偽通道(pseudo channel),那么就一共有32個pseudo channel。HBM存儲大小分為64Gb和128Gb,所以最大為16GB。

我個人對于HBM的理解,如果在應用層面,可以認為HBM是32個堆疊的DDR,每個DDR應用AXI3總線協議,使用起來和控制DDR也非常相似。

HBM結構

HBM的地址空間

HBM的32個pseudo channel都是使用axi3協議,所以指令和數據的傳輸方式也和DDR相同,本文主要講解一下不同點,也就是HBM的地址空間。

以4H(內存大小64Gb)的HBM為例:

Bit[32]用于區分左右stack;

Bit[31:28]用于選擇每個stack里面16個pseudo channel的哪一個axi總線;

Bit[27:5]為有效地址部分;

Bit[4:0]為無用比特位,原因是數據位寬為256bit,每次都要最少傳輸256bit,那么就需要32Byte對齊,所以其低5bit永遠為0。

具體使用方法

使用過程中用axi3總線協議,其實可以不完全按照IP手冊中所要求的地址空間進行設置,上文所述的地址空間更像是只給了整個HBM一個AXI接口,但是Xilinx自己的IP核連接過程中也是用了32個AXI接口(假如用了1個HBM的32個通道)。所以我們在使用過程中,可以直接例化32個AXI總線接口,與32個AXI接口的通道連接,地址空間完全可以只有28比特,也就是6+22,這樣就不需要高5比特的通道選擇比特位了。

HBM其他特點

不支持fixed addressing mode(AXI3協議不支持)。

fixed的burst模式代表,對同一個地址進行burst讀寫,本人也沒有用過這個場景,并且在axi3中也是不支持的,暫時猜測這種場景可能是,地址用于片選,后面跟著幾個FIFO,然后burst傳輸給對應片選的FIFO數據。

burstlength位寬為4比特,最大為16。

HBM每一個原始的channel時鐘頻率是900MHz,但是卻把每一個channel拆分成兩個pseudo channel,時鐘降頻為450MHz。這樣做對于HBM端口的吞吐量沒有變化,但是接口時鐘降低了一半,這樣做更有利于后續FPGA處理和計算,防止timing問題導致不能應用900MHz的時鐘頻率。那么后續我們在使用過程中,也可以將256bit數據合為512bit,這樣可以將數據頻率再降低一半, 也是一種適配計算頻率不高場景的方法。