先進封裝技術介紹--高帶寬架構(HBF,High Bandwidth Fabrics)

轉:

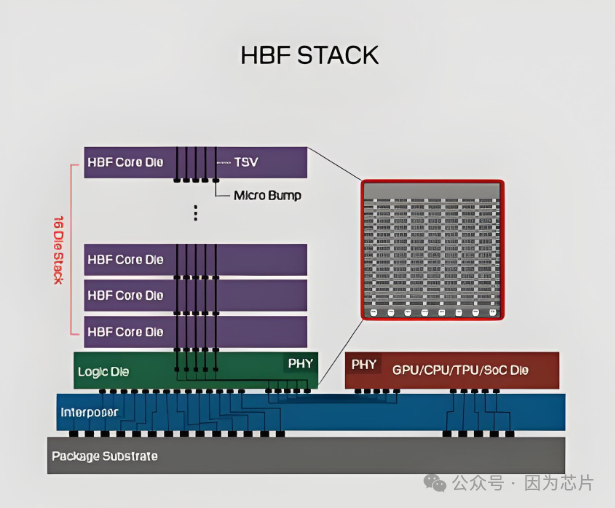

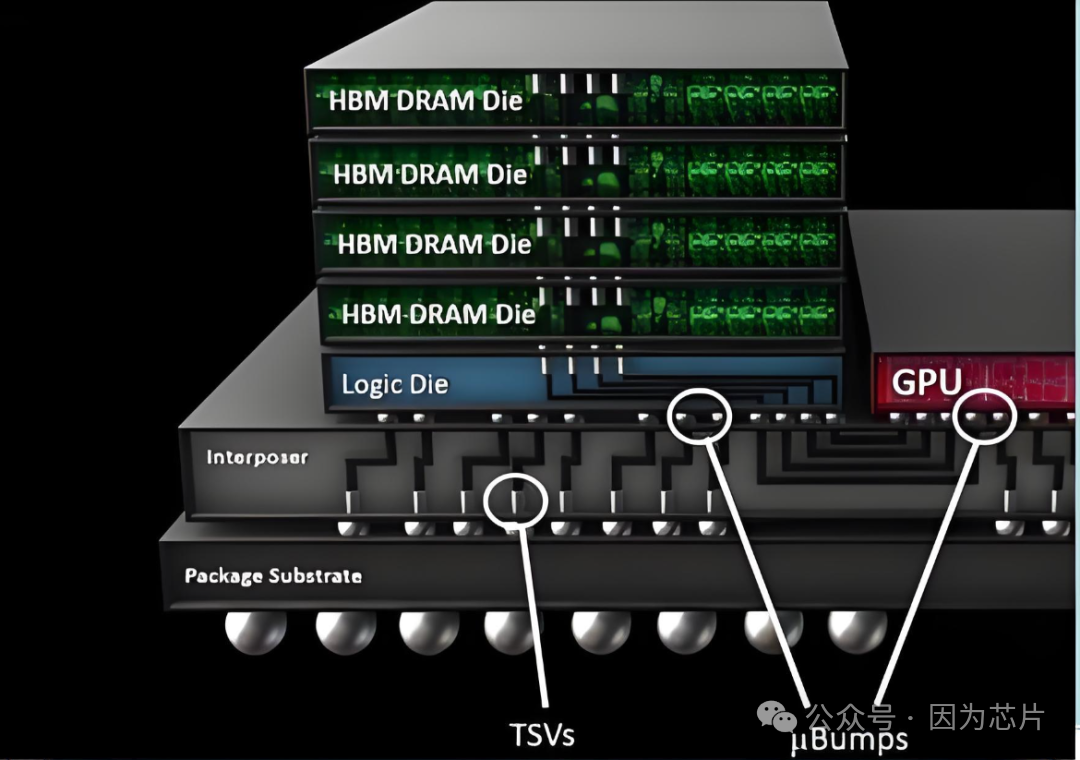

HBF 是 High Bandwidth Fabrics 的縮寫,直譯為“高帶寬架構”。它是一種由 英特爾 提出并主導的先進封裝技術和互連標準。其核心目標是在一個封裝內,將多個芯片(如計算芯片、內存、I/O芯片等)通過一個超高帶寬、低功耗、低延遲的片上互連網絡連接起來,形成一個高性能的“超級芯片”。

簡單理解:HBF 就像是在一個“微型主板”上,為各個芯片構建了一個超級高速公路網,讓它們能以極高的速度和效率交換數據。

最基礎的“能否裝得下、連得上”的規(guī)則。 凸塊與間距規(guī)則: 凸塊類型:明確允許使用的互連類型(如微凸塊用于標準連接,銅柱或混合鍵合用于Foveros Direct)。 凸塊間距:規(guī)定最小凸塊中心距(例如,標準微凸塊為35-55μm,混合鍵合可達<10μm)。這直接決定了互連密度和帶寬。 凸塊陣列布局:規(guī)定芯粒邊緣必須留出非功能凸塊(啞凸塊) 用于機械支撐,以及電源/接地凸塊的分布比例和模式。 芯粒與硅橋布局規(guī)則: 芯粒尺寸和形狀限制:對芯粒的最大/最小尺寸、長寬比、以及邊緣到有效電路的距離(切割道)有明確規(guī)定。 芯粒到芯粒間距:規(guī)定兩個相鄰芯粒之間的最小距離(芯片到芯片間隙),以確保有足夠空間填充下填料,并避免熱機械應力干擾。 硅橋對準容差:規(guī)定芯粒上的凸塊陣列與下方硅橋上的焊盤之間允許的最大對準誤差(通常為±1~2μm)。這直接影響設計的余量和良率。 “Keep-out Zone”規(guī)則: 在芯粒的特定區(qū)域(如靠近邊緣、靠近高熱模塊處)禁止放置敏感電路或關鍵信號凸塊,以規(guī)避應力、熱梯度或封裝效應的不利影響。

對比維度 HBM(高帶寬內存) HBF(高帶寬互連架構) 中文全稱 英文全稱 本質屬性 存儲器芯片產品 封裝互連技術平臺 技術范疇 核心功能 供應形式 對比維度 HBM HBF 核心技術 連接方式 密度提升方式 接口特性 物理形態(tài) 制造工藝 代表產品/技術 參數類型 HBM典型值/特征 HBF典型值/特征 連接密度 物理間距 傳輸延遲 能效比 帶寬規(guī)模 工藝節(jié)點 溫度特性 際發(fā)展 HBM演進 HBF演進 第一代

? 4層堆疊

? 128GB/s帶寬

? 基礎硅橋

? 2D平面連接第二代

? 8層堆疊

? 256GB/s帶寬

? 3D堆疊技術

? 芯片上堆疊芯片第三代

? 8-12層堆疊

? 460GB/s帶寬

? 多芯粒3D集成

? 混合封裝技術第四代

? 16層堆疊

? 819GB/s帶寬

? 混合鍵合技術

? <10μm凸塊間距發(fā)展趨勢

? 帶寬密度提升

? 能效比優(yōu)化

? 支持更多芯粒集成

? 向chiplet生態(tài)系統(tǒng)演進